Зворотна мережа доставлення живлення (BS PDN) для мікросхем наступного покоління є добре відомою та широко обговорюваною перевагою технології майбутнього. У той час як Intel і TSMC деякий час говорили про BSPDN, Samsung лише нещодавно поділився подробицями про свої експерименти з живленням. Схоже, компанія очікує від цього нововведення досить помітних переваг.

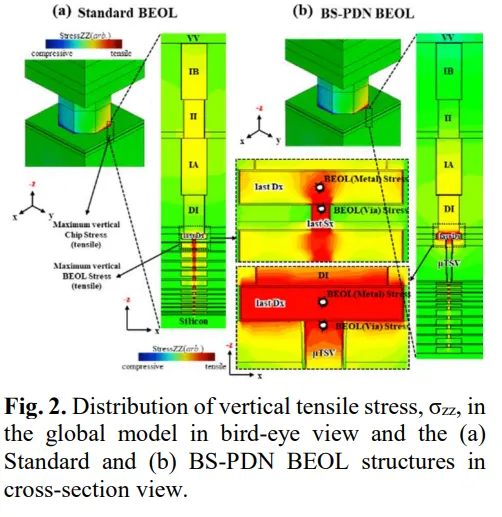

У статті, представленій на симпозіумі VLSI наприкінці червня, Samsung Electronics повідомила, що застосування задньої мережі живлення призвело до зменшення на 14,8% площі нерозкритого процесора порівняно з традиційним фронтальним PDN, повідомляє The El. Між тим, у документі спеціально виділено два контури Arm, де вони спостерігали зменшення площі на 10,6% і 19% відповідно. Зменшення площі кристала на 10-19% є великою перевагою, оскільки це дає змогу або упакувати на 10-19% більше транзисторів і підвищити продуктивність, або знизити вартість конкретного чіпа.

Ще одна річ, яку Samsung згадав у своїй статті, це зменшення довжини проводів на 9,2%. Задня шина живлення зазвичай дозволяє використовувати більш товсті дроти з меншим опором і, отже, може створювати більші струми для кращої продуктивності. Подальше зменшення довжини дроту також принесе додаткові переваги продуктивності.

Додаткові переваги, які сприяють подачі живлення на задній панелі, які показала компанія Samsung, — це ручки спільної оптимізації технології дизайну, які дозволили покращити Fmax на 3,6%, зменшити площу стандартного блоку на 2,4% і покращити продуктивність стандартного блоку на 1,6%.

Раніше в цьому році Intel детально описала свою задню мережу живлення PowerVia, яка використовуватиметься для її технології виробництва 20A (клас 2 нм) і не тільки. Переваги використання задньої шини живлення широко визнані, і висновки Samsung підтверджують цю теорію. Проводи живлення можна зробити більш значними, перемістивши шини живлення назад та ізолюючи їх від проводки вводу/виводу. Це потовщення зменшує опір на кінцевих етапах виробництва, підвищуючи продуктивність і зменшуючи споживання енергії. Крім того, це розділення призводить до зменшення логічної області, що призводить до економії коштів.

Samsung не розкриває, коли вона планує реалізувати свій BS PDN і з яким вузлом. Наразі компанія вдосконалює свою технологію виробництва SF3 3-нм класу 3-нанометрового класу на основі SF3-транзисторів 2-го покоління та планує використовувати її для масового виробництва у 2024 році. Компанія також має SF3P і 2-нм-клас SF2, які повинні бути випущені у 2025 році. Малоймовірно, що Samsung використовуватиме задню шину живлення для SF3 наступного року, компанія може розглянути можливість впровадження свого BS PDN у SF3P або SF2 у 2025 році.

Залишайтеся на передовій

Приєднуйтеся до експертів, які читають Tom’s Hardware для внутрішньої інформації про новини ПК для ентузіастів — і так уже понад 25 років. Ми надсилатимемо екстрені новини та докладні огляди процесорів, графічних процесорів, штучного інтелекту, апаратного забезпечення виробника тощо прямо до вашої скриньки. Джерело